# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

## FEATURES AND BENEFITS

- Directly interfaces with strain gauge or other transducer in Wheatstone bridge configuration for low noise and high accuracy measurements

- On-chip Poly(4,4) compensation for improved accuracy over temperature, compensating both IC and bridge

- Offering from Poly(1,1) to Poly(4,4) polynomial compensation including any possible degree between 0 and 4 like Poly(2,4) and Poly(3,3).

- · Ratiometric analog output for legacy applications

- High bandwidth option to support fast response time applications

- PWM (Pulse-Width Modulated) output with optional diagnostics to identify fault conditions

- SENT (Single-Edge Nibble Transmission) output configurable for temperature or diagnostic reporting in addition to pressure data

- Fast SENT provides increased data rates to support fast response time applications

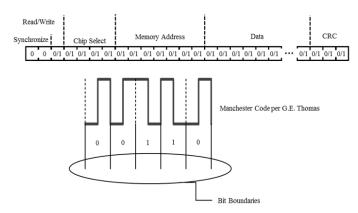

- Manchester interface for programming through single OUT pin

- Internal device temperature available on output via SENT protocol (or volatile registers)

- Suite of diagnostics to allow for safety-critical systems fault detection

- Broken wire detection

- Under- and overvoltage detection

- Under- and overtemperature detection

Continued on next page ...

## DESCRIPTION

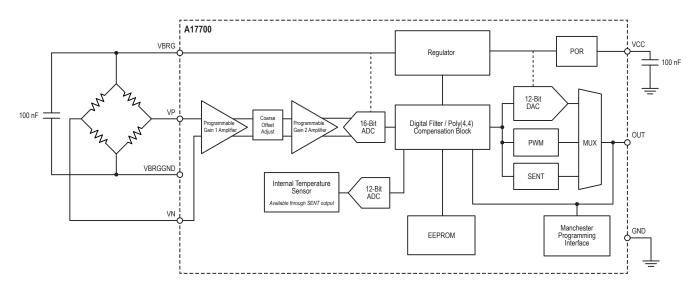

The A17700 is a sensor interface IC designed to connect directly to a strain gauge or other sensor in a Wheatstone bridge configuration. The A17700 amplifies and converts the analog input from the bridge to the digital domain, low-pass filters the signal, and outputs a ratiometric analog signal or a digital SENT/PWM protocol. Digital signal processing functions, including temperature compensation and gain/offset trim, provide an accurate and linear output. A Manchester programming interface for configurations is also available. It includes on-chip EEPROM technology capable of supporting up to 100 read/write cycles for programming of calibration parameters.

The A17700 incorporates advanced diagnostic functions to support safety-critical application designs.

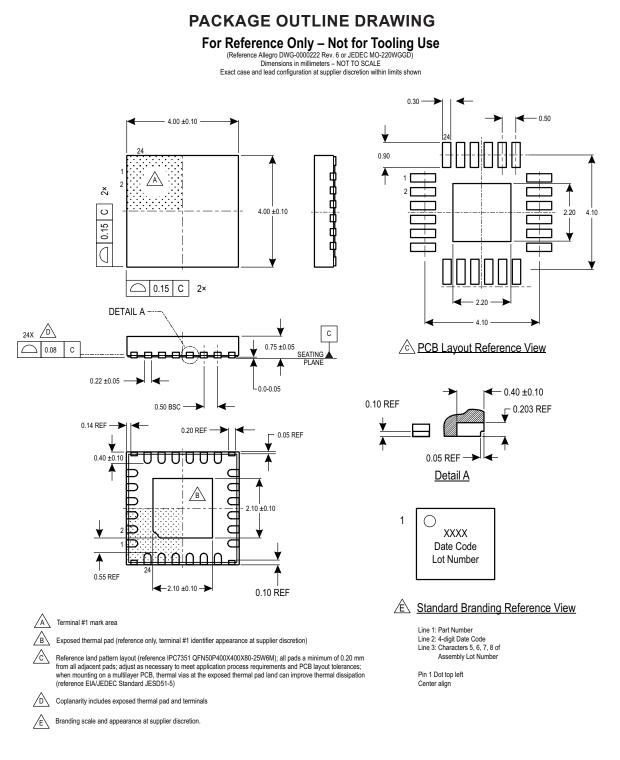

The A17700 is available in a 24-pin 4 mm  $\times$  4 mm QFN package with wettable flank and exposed thermal pad.

### PACKAGE:

24-pin wettable flank QFN with exposed thermal pad (suffix ES)

#### Figure 1: Functional Block Diagram

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

## FEATURES AND BENEFITS (continued)

- Bridge diagnostics

- Input signal Out-of-Range detection

- EEPROM with Error Correction Control (ECC) for trimming capability and product traceability

- AEC-Q100 Grade 0

- Wide operating temperature range: -40°C to 150°C

- QFN package with redundant bridge supply pins for PCB board space optimization

- · Wettable flanks enabling visual inspection of solder joints

#### SELECTION GUIDE

| Part Number Output |                           | Packing                                                | Packing                     |  |

|--------------------|---------------------------|--------------------------------------------------------|-----------------------------|--|

| A17700LESBTR-AO    | Analog Output             | 24-pin QFN with wettable flank and exposed thermal pad | 1500 pieces per 7-inch reel |  |

| A17700LESBTR-DO    | Digital Output (SENT/PWM) | 24-pin QFN with wettable flank and exposed thermal pad | 1500 pieces per 7-inch reel |  |

#### **ABSOLUTE MAXIMUM RATINGS**<sup>[1]</sup>

| Characteristic                                | Symbol              | Notes                                                        | Rating     | Unit |

|-----------------------------------------------|---------------------|--------------------------------------------------------------|------------|------|

| Forward Supply Voltage                        | V <sub>CC</sub>     |                                                              | 24         | V    |

| Reverse Supply Voltage                        | V <sub>RCC</sub>    | Voltage delta between supply and output must not exceed 24 V | -18        | V    |

| Output Pin Forward Voltage                    | V <sub>OUT</sub>    | Voltage delta between supply and output must not exceed 24 V | 24         | V    |

| All Other Pins Forward Voltage [2]            | V <sub>IN</sub>     |                                                              | 3.6        | V    |

| Output and All Other Pins Reverse Voltage [2] | V <sub>R</sub>      |                                                              | -0.5       | V    |

| Operating Ambient Temperature                 | T <sub>A</sub>      | L range                                                      | -40 to 150 | °C   |

| Maximum Junction Temperature                  | T <sub>J(max)</sub> |                                                              | 165        | °C   |

| Storage Temperature                           | T <sub>stg</sub>    |                                                              | -65 to 170 | °C   |

<sup>[1]</sup> Stresses beyond the Absolute Maximum Ratings may result in permanent device damage.

<sup>[2]</sup> "All Other Pins" refer to the pins that are driven by the device and should not be connected to external supplies.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions, see application information

| Characteristic             | Symbol           | Test Conditions [3]                      |    | Unit |

|----------------------------|------------------|------------------------------------------|----|------|

| Deskens Themsel Desistence | Р                | Single-layer PCB based on JEDEC standard |    | °C/W |

| Package Thermal Resistance | κ <sub>θJA</sub> | Four-layer PCB based JEDEC standard      | 37 | °C/W |

<sup>[3]</sup> Additional thermal information available on the Allegro website.

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

## **Table of Contents**

| Features and Benefits                        | 1  |

|----------------------------------------------|----|

| Description                                  | 1  |

| Package                                      | 1  |

| Functional Block Diagram                     | 1  |

| Selection Guide                              | 2  |

| Absolute Maximum Ratings                     | 2  |

| Thermal Characteristics                      | 2  |

| Pinout Diagram and Terminal List             | 4  |

| Operating Characteristics                    |    |

| Functional Description                       |    |

| Bandwidth Selection                          | 10 |

| Output Response Time                         | 10 |

| Power-On Time                                |    |

| Front End Gain Adjustment                    |    |

| Front End Differential Offset Adjustment     | 11 |

| Input Signal Range Calculation               |    |

| Fine Adjustment and Temperature Compensation |    |

| Output Protocols                          | 14 |

|-------------------------------------------|----|

| Digital Output Mode Selection             | 18 |

| Digital Output Driver Fall Time Selection |    |

| Broken Wire Detection                     | 18 |

| Diagnostic Features                       | 18 |

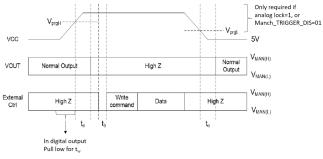

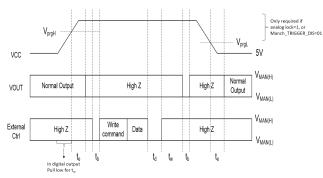

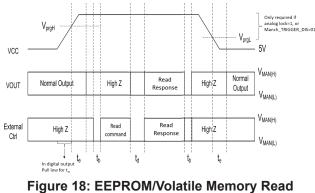

| Programming: Manchester Communication     | 21 |

| Entering Manchester Coding                |    |

| Manchester Interface Message Structure    |    |

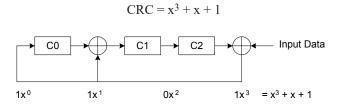

| CRC                                       | 24 |

| Device Access                             |    |

| Shadow Registers                          |    |

| Device EEPROM and Register Access Lock    |    |

| EEPROM Map                                |    |

| Volatile Registers Map                    |    |

| Power Derating                            |    |

| Package Outline Drawing                   |    |

|                                           |    |

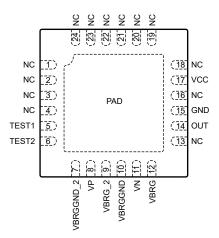

## **PINOUT DIAGRAMS AND TERMINAL LIST**

Package ES, 24-Pin QFN Pinout Diagram

#### **Terminal List Table**

| Number   | Name Function |                                           |

|----------|---------------|-------------------------------------------|

| 1 to 4   | NC            | No internal connection <sup>[1]</sup>     |

| 5        | TEST1         | Factory Test Pin 1; connect to GND        |

| 6        | TEST2         | Factory Test Pin 2; connect to GND        |

| 7        | VBRGGND_2     | 2nd GND pin for the bridge <sup>[2]</sup> |

| 8        | VP            | Positive bridge output                    |

| 9        | VBRG_2        | 2nd bridge supply pin [3]                 |

| 10       | VBRGGND       | GND pin for the bridge                    |

| 11       | VN            | Negative bridge output                    |

| 12       | VBRG          | Bridge supply                             |

| 13       | NC            | No internal connection <sup>[1]</sup>     |

| 14       | OUT           | Analog / open drain output                |

| 15       | GND           | Ground                                    |

| 16       | NC            | No internal connection <sup>[1]</sup>     |

| 17       | VCC           | Supply voltage                            |

| 18 to 24 | NC            | No internal connection <sup>[1]</sup>     |

| _        | PAD           | Exposed thermal pad                       |

[1] For increased ESD performance, connect NC (no connection) pins to GND.

[2] This is a second ground pin for the bridge intended for single layer PCB design.

Internally connected to VBRGGND. Connect to GND if not used.

<sup>[3]</sup> This is a second bridge supply pin intended for single layer PCB design. Internally connected to VBRG. Leave floating if not used.

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

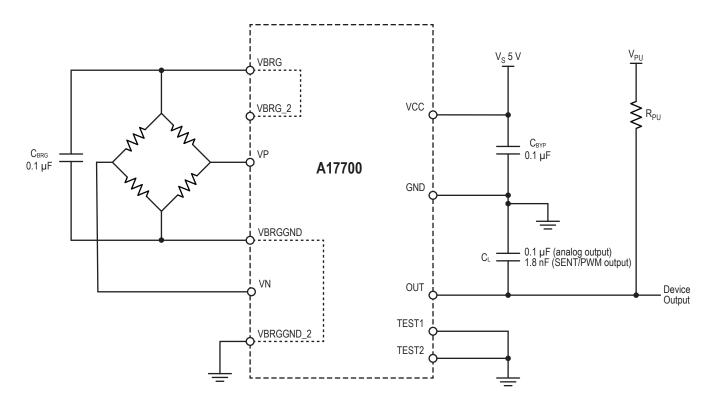

**Figure 2: Typical Application Circuit**

Note: VBRG and VCC decoupling caps must be mounted as close as possible to device package. For increased ESD performances, connect NC (no connection) pins to GND.

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

| Characteristics                                             | Characteristics Symbol Test Conditions |                                                                                                                      | Min. | Тур.  | Max. | Unit |

|-------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| ELECTRICAL CHARACTERISTICS                                  |                                        |                                                                                                                      |      |       |      |      |

| Supply Voltage                                              | V <sub>CC</sub>                        |                                                                                                                      | 4.5  | 5     | 5.5  | V    |

| Supply Current                                              | I <sub>CC</sub>                        | Excluding external bridge and output load                                                                            | _    | 6     | 10   | mA   |

| Supply Zener Clamp Voltage                                  | V <sub>Zsup</sub>                      | $I_{CC} = I_{CC(max)} + 30 \text{ mA}; T_A = 25^{\circ}C$                                                            | 24   | -     | _    | V    |

| Reverse Supply Zener Clamp Voltage                          | V <sub>RZsup</sub>                     | I <sub>CC</sub> = –25 mA; T <sub>A</sub> = 25°C                                                                      | _    | -     | -18  | V    |

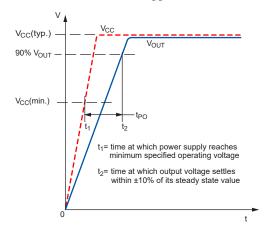

| Power-On Time <sup>[1]</sup>                                | t <sub>PO</sub>                        | Time between min V <sub>CC</sub> reached and analog<br>output reaches 90% of final value;<br>bandwidth (BW) >1.2 kHz | _    | _     | 1    | ms   |

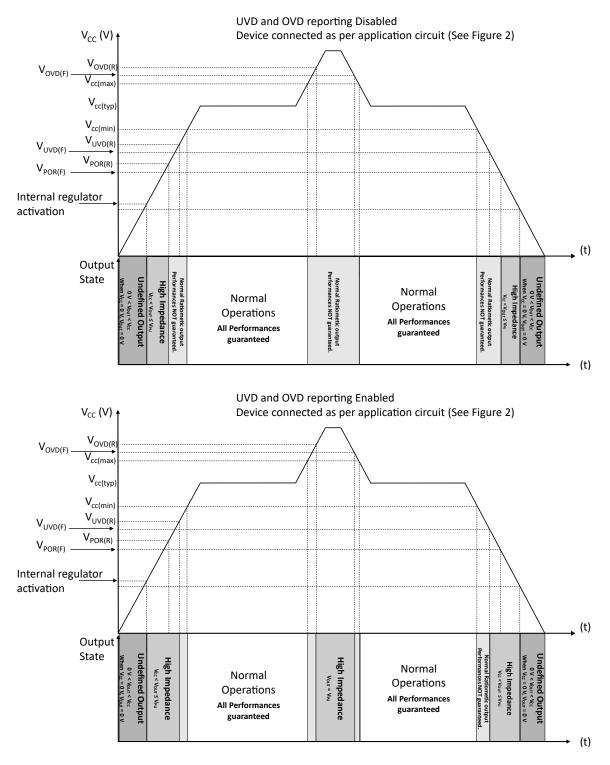

|                                                             | V <sub>POR(R)</sub>                    | V <sub>CC</sub> rising; see Figure 3                                                                                 | 3.6  | -     | 4.0  | V    |

| Power-On Reset Voltage                                      | V <sub>POR(F)</sub>                    | V <sub>CC</sub> falling; see Figure 3                                                                                | 3.3  | -     | 3.8  | V    |

|                                                             | V <sub>POR(hys)</sub>                  | Hysteresis                                                                                                           | 100  | _     | 500  | mV   |

|                                                             | V <sub>UVD(R)</sub>                    | $V_{CC}$ rising, $T_A = 25^{\circ}C$ ; see Figure 3                                                                  | 4.1  | _     | 4.5  | V    |

| Undervoltage Detection                                      | V <sub>UVD(F)</sub>                    | $V_{CC}$ falling, $T_A = 25^{\circ}C$ ; see Figure 3                                                                 | 4.0  | _     | 4.4  | V    |

|                                                             | V <sub>UVD(hys)</sub>                  | Hysteresis                                                                                                           | 70   | _     | 500  | mV   |

|                                                             | V <sub>OVD(R)</sub>                    | $V_{CC}$ rising, $T_A = 25^{\circ}C$ ; see Figure 3                                                                  | 5.7  | _     | 6    | V    |

| Overvoltage Detection                                       | V <sub>OVD(F)</sub>                    | V <sub>CC</sub> falling, T <sub>A</sub> = 25°C; see Figure 3                                                         | 5.5  | _     | 5.8  | V    |

|                                                             | V <sub>OVD(hys)</sub>                  | Hysteresis                                                                                                           | 100  | _     | 500  | mV   |

| Initial Bandwidth <sup>[1]</sup>                            | BW <sub>2.5</sub>                      | Default bandwidth setting                                                                                            | _    | 2.5   | _    | kHz  |

| Programmable Operating<br>Bandwidth Range <sup>[1][2]</sup> | BW <sub>prog</sub>                     | Set by programming the digital low-pass filter                                                                       | 0.3  | _     | 20   | kHz  |

| Initial Output Response Time [2]                            | t <sub>resp-Init</sub>                 | Bandwidth option: BW <sub>2.5</sub>                                                                                  | _    | 250   | _    | μs   |

| BRIDGE ELECTRICAL CHARACTE                                  |                                        | ·,                                                                                                                   |      |       |      |      |

| Bridge Supply Voltage                                       | V <sub>BRG</sub>                       | Voltage supplied to transducer bridge                                                                                | 3.15 | 3.3   | 3.45 | V    |

| Bridge Resistance                                           | R <sub>BRG</sub>                       | Resistance of transducer bridge                                                                                      | 1.5  | _     | 10   | kΩ   |

| Bridge Bypass Capacitor                                     | C <sub>BRG</sub>                       | Bypass capacitor                                                                                                     | 80   | 100   | 150  | nF   |

| ANALOG FRONT END CHARACTE                                   |                                        |                                                                                                                      |      |       |      |      |

| Differential Input (V <sub>P</sub> -V <sub>N</sub> )        | V <sub>IN</sub>                        | Gain1 = 3×, Gain2 = 1×, Offset <sub>coarse</sub> = 0,<br>$V_{BRG}$ = 3.3 V                                           | -290 | _     | 290  | mV   |

| ADC Input Range [3]                                         | ADC <sub>IN</sub>                      |                                                                                                                      | -263 | _     | 263  | mV/V |

| Bridge Sensitivity <sup>[1][3]</sup>                        | BRG <sub>sens</sub>                    | V <sub>P</sub> -V <sub>N</sub> at maximum input stimulus                                                             | 10   | _     | 80   | mV/V |

|                                                             |                                        | Gain1 Trim bits                                                                                                      | _    | 2     | _    | bits |

| Bridge Sensitivity Programming Bits                         | -                                      | Gain2 Trim bits                                                                                                      | _    | 4     | _    | bits |

| Bridge Offset [1][3]                                        | OFFSET <sub>coarse</sub>               | Differential output offset, $V_P$ - $V_N$ , no input stimulus;<br>Scales with Gain1; Gain1 = 3×; see Table 4         | -80  | _     | 80   | mV/V |

| Bridge Offset Programming Bits                              | -                                      | Number of Offset trim bits                                                                                           | -    | 6     | -    | bits |

| Bridge Offset Programming Step Size                         | OFFSET <sub>stp</sub>                  | Scales with Gain1; Gain1 = 3×; see Table 4                                                                           | _    | 2.667 | _    | mV/V |

| Polarity Bit                                                | pol bit                                | Inverts the polarity of bridge input, in digital domain                                                              | _    | 1     | _    | bit  |

<sup>[1]</sup> Guaranteed by design. Not tested in production.

<sup>[2]</sup> See Bandwidth selection in Functional Description section for details.

[3] Analog front end gain and differential offset can be adjusted to adapt the bridge signal to the chip ADC input range. Note that offset scales with Gain 1 (Table 4). See Front End Gain and Offset Adjustment or Input Signal range calculation sections for details.

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

#### OPERATING CHARACTERISTICS: Valid over the full supply voltage and ambient temperature ranges, unless otherwise noted

| Characteristics                                             | Symbol                     | Test Conditions                                                                                                                                                                                   |     | Тур. | Max.            | Unit              |  |

|-------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----------------|-------------------|--|

| ANALOG OUTPUT CHARACTERISTICS                               |                            |                                                                                                                                                                                                   |     |      |                 |                   |  |

| Analog Output Effective Resolution [1]                      | RES <sub>OUT</sub>         | Across entire code range, theoretical noise-free<br>input, BW = 2.5 kHz; Gain1 = 3× (default)                                                                                                     | -   | 12.8 | _               | bits              |  |

| Angler Output Clarge Dange [1]                              | V <sub>CLAMP(HIGH)</sub>   | $V_{CC} = 5 \text{ V}, \text{ R}_{PD} \ge 4.4 \text{ k}\Omega \text{ or } \text{ R}_{PU} \ge 4.4 \text{ k}\Omega;$<br>see Table 7                                                                 | 70  | _    | 96              | % V <sub>CC</sub> |  |

| Analog Output Clamp Range [1]                               | V <sub>CLAMP(LOW)</sub>    | $V_{CC} = 5 \text{ V}, \text{ R}_{PU} \ge 4.4 \text{ k}\Omega \text{ or } \text{R}_{PD} \ge 4.4 \text{ k}\Omega;$ see Table 7                                                                     | 4   | _    | 30              | % V <sub>CC</sub> |  |

| Analog Output Clamp<br>Programming Step Size <sup>[1]</sup> | V <sub>CLAMP(STP)</sub>    | Valid for $V_{\text{CLAMP}(\text{HIGH})}$ and $V_{\text{CLAMP}(\text{LOW})}$                                                                                                                      | -   | 1    | _               | % V <sub>CC</sub> |  |

| Analog Output Clamp Low Value                               | V <sub>LIMCLAMP(LOW)</sub> | V <sub>CC</sub> = 5 V, 1.1 mA forced to output,<br>Clamp_Low code 0 (default)                                                                                                                     | 0.1 | 0.2  | 0.3             | V                 |  |

| Analog Output Clamp High Value                              | VLIMCLAMP(HIGH)            | V <sub>CC</sub> = 5 V, 1.1 mA forced to output,<br>Clamp_High code 0 (default)                                                                                                                    | 4.7 | 4.8  | 4.9             | V                 |  |

| Analog Output Load Capacitance [2]                          | CL                         |                                                                                                                                                                                                   | 10  | 100  | 120             | nF                |  |

| Maximum Sourcing Current                                    | I <sub>source</sub>        |                                                                                                                                                                                                   | 10  | -    | 30              | mA                |  |

| Maximum Sink Current                                        | I <sub>sink</sub>          |                                                                                                                                                                                                   | 10  | -    | 30              | mA                |  |

| Output Slew Rate [1]                                        | SR                         | I <sub>source</sub> = 10 mA, C <sub>L</sub> = 100 nF                                                                                                                                              | _   | -    | 100             | V/ms              |  |

| Analog Output Load Resistance                               | R <sub>PU</sub>            | Pull-up or pull-down resistor                                                                                                                                                                     | 4.4 | 10   | _               | kΩ                |  |

| Output Noise [1]                                            | V <sub>OUTnoise</sub>      | $V_{DD\_DAC} = 5.0 \text{ V}, BW = 2.5 \text{ kHz}, T_A = 25^{\circ}\text{C}, C_L = 100 \text{ nF}; DC \text{ input signal; } V_P = V_N; Gain1 = 3^{\circ} (default) and Gain2 = 7^{\circ} (max)$ | _   | 0.65 | _               | mV <sub>RMS</sub> |  |

| DC Output Impedance [1][3]                                  | R <sub>OUT</sub>           | $T_A = 25^{\circ}C$                                                                                                                                                                               | _   | 1    | _               | Ω                 |  |

| Analog Output Ratiometry Error [1]                          | Rat <sub>Err</sub>         | Across specified V <sub>CC</sub> range; relative to V <sub>CC</sub> = 5 V;<br>output range from 10% to 90% V <sub>CC</sub> ;<br>Gain1 = 3× (default)                                              | _   | ±0.2 | _               | %                 |  |

| Output Linearity <sup>[1]</sup>                             | Lin <sub>ERR</sub>         | Full-Scale Linearity Error (INL);<br>output range from 10% to 90% V <sub>CC;</sub><br>Gain1 = 3× (default), Gain2 = 1×                                                                            | _   | ±0.2 | _               | %V <sub>CC</sub>  |  |

| Overall Accuracy [1][4]                                     | -                          | Over lifetime and temperature—Full signal path;<br>Gain1 = 3× (default), Gain2 = 1×                                                                                                               | -   | ±0.3 | _               | %V <sub>CC</sub>  |  |

| Pull-Up Voltage                                             | V <sub>PU</sub>            | Connected as per typical application circuit                                                                                                                                                      | _   | -    | V <sub>CC</sub> | V                 |  |

| BROKEN WIRE CHARACTERISTI                                   | CS                         | · · · · ·                                                                                                                                                                                         |     |      |                 |                   |  |

| Analog Output Diagnostic Saturation                         | V <sub>sat_diag_H</sub>    | V <sub>CC</sub> = 5 V, broken GND, I <sub>OUT(source)</sub> = 1.1 mA                                                                                                                              | 4.7 | 4.9  | 5.0             | V                 |  |

| Voltage (Broken Wire Detection)                             | V <sub>sat_diag_L</sub>    | V <sub>CC</sub> = 5 V, broken VCC, I <sub>OUT(sink)</sub> = 1.1 mA                                                                                                                                | 0.0 | 0.1  | 0.3             | V                 |  |

<sup>[1]</sup> Guaranteed by design. Not tested in production.

<sup>[2]</sup> Larger output load capacitance up to 330 nF is not tested in production but can be handled by the device with DAC Output Cap driver EEPROM parameter set to code 2 (See EEPROM MAP).

<sup>[3]</sup> Output impedance given for frequencies < 400 Hz.

<sup>[4]</sup> Overall accuracy considers ideal compensation over temperature and full Wheatstone bridge (all four resistors changing depending on sensed stress).

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

#### OPERATING CHARACTERISTICS: Valid over the full supply voltage and ambient temperature ranges, unless otherwise noted

| Characteristics                 | Symbol                    | Test Conditions                                                                     | Min. | Тур.  | Max.            | Unit |

|---------------------------------|---------------------------|-------------------------------------------------------------------------------------|------|-------|-----------------|------|

| PWM / SENT OUTPUT               |                           | · · · · · ·                                                                         |      |       |                 |      |

| Output Load Resistance          | R <sub>PU</sub>           | Pull-up resistor; output current ≥ –10 mA                                           | 1.2  | _     | _               | kΩ   |

| External Load Capacitor         | CL                        | Open-drain output mode                                                              | _    | _     | 4.7             | nF   |

| Output Low Saturation Voltage   | V <sub>OUT(Sat)LOW</sub>  | Output current = -4.7 mA, V <sub>CC</sub> = 5 V,<br>Output FET on                   | _    | -     | 0.35            | V    |

| Output Leakage Current          | -                         | Output voltage ≤ 5.5 V, output FET off,<br>Open-drain output mode                   | _    | -     | 10              | μA   |

| Output High Saturation Voltage  | V <sub>OUT(Sat)HIGH</sub> | Output current = 4.7 mA, V <sub>CC</sub> = 5 V, Output FET<br>Push-pull output mode | 4.3  | -     | _               | V    |

| Output Current Limit            | I <sub>LIMIT</sub>        |                                                                                     | 18   | 25    | 35              | mA   |

| Pull-Up Voltage                 | V <sub>PU</sub>           |                                                                                     | _    | -     | V <sub>CC</sub> | V    |

| Overall Digital Output Accuracy | -                         |                                                                                     | _    | 0.3   | _               | %    |

| PWM INTERFACE SPECIFICATION     | ONS                       | · · · · · · · · · · · · · · · · · · ·                                               |      |       |                 |      |

| PWM Carrier Frequency           | f <sub>PWM</sub>          | Programmable through EEPROM;<br>See description section                             | 0.25 | _     | 16              | kHz  |

| PWM Clamp Programming Range     | PWM <sub>CLAMP(H)</sub>   |                                                                                     | _    | _     | 96              | %DC  |

|                                 | PWM <sub>CLAMP(L)</sub>   |                                                                                     | 4    | -     | _               | %DC  |

| PWM Resolution <sup>[1]</sup>   |                           | Noise-free input, f <sub>PWM</sub> ≤ 2.67 kHz                                       | _    | 12    | _               | bits |

|                                 | RES <sub>PWM</sub>        | Noise-free input, f <sub>PWM</sub> ≤ 16 kHz                                         | _    | 9     | _               | bits |

| PWM Output Jitter [1]           | PWM <sub>JIT</sub>        | Noise-free input, f <sub>PWM</sub> ≤ 2.67 kHz                                       | _    | 0.025 | _               | %DC  |

|                                 |                           | Noise-free input, f <sub>PWM</sub> ≤ 16 kHz                                         | _    | 0.18  | _               | %DC  |

| PWM Carrier Frequency Tolerance | f <sub>PWM-tol</sub>      |                                                                                     | -10  | _     | 10              | %    |

| SENT INTERFACE SPECIFICATIO     | NS                        |                                                                                     |      |       |                 |      |

| SENT Tick Time <sup>[2]</sup>   | t <sub>TICK</sub>         | Programmable through EEPROM; see description section                                | 0.5  | _     | 5               | μs   |

| SENT Tick Time Tolerance        | TOL <sub>tick</sub>       |                                                                                     | -10  | -     | 10              | %    |

| SENT Message Duration           | t <sub>SENT</sub>         | Tick time = 3 µs                                                                    | _    | -     | 1               | ms   |

| Fast SENT Message Duration      | t <sub>SENTMIN</sub>      | Tick time = 0.5 μs, 3 data nibbles, SCN, and CRC, nibble length = 27 ticks          | _    | 96    | _               | μs   |

| INTERNAL TEMPERATURE OUTP       | UT THROUGH                | SENT                                                                                |      |       |                 |      |

| Internal Temperature Range      | T <sub>SENT-Range</sub>   | 12-bit digital temperature                                                          | -256 | _     | 255             | °C   |

| Internal Temperature Resolution | T <sub>SENT-step</sub>    | Internal temperature sensor output digital step                                     | _    | 0.125 | _               | °C   |

<sup>[1]</sup> Guaranteed by design. Not tested in production.

<sup>[2]</sup> See Table 6 in Functional Description section for details.

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

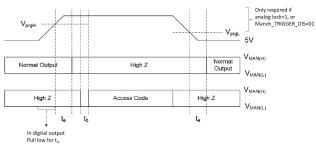

Figure 3: Output Behavior Under V<sub>CC</sub> Ramp Conditions

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

## FUNCTIONAL DESCRIPTION

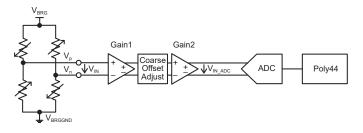

The A17700 is a signal conditioning IC that accepts a differential Wheatstone bridge input. The bridge signal is amplified with a programmable gain amplifier, and a coarse offset is applied. The purpose of this front end is to fill the ADC range as much as possible, but also ensure that the ADC is not saturated over temperature and operating conditions. The DSP logic will then provide a filter to reduce noise (also setting the effective operating bandwidth of the device) to the application bandwidth and apply fine signal adjustments and temperature compensation through polynomial equation (up to  $poly_{4,4}$ ). The output can be selected between ratiometric analog output, SENT, or PWM.

### **Bandwidth Selection**

The internal filter bandwidth can be adjusted to minimize output noise and improve resolution in function of the system bandwidth. The choice of bandwidth will be a compromise between response time and system resolution. Table 1 is provided to help define better option for the system.

#### Table 1: Bandwidth Selection Table **Ideal Noise-Free** Typical Bandwidth **Resolution at Given** Bandwidth Response Bandwidth (2.2 kΩ bridge Code Time and 25 mV/V sensitivity) 0 (Default) 2.5 kHz 13.7 bits 250 µs 1 0.3 kHz 1350 µs 15.0 bits 2 0.6 kHz 750 µs 14.6 bits 3 1.0 kHz 470 µs 14.4 bits 4 2.5 kHz 13.7 bits 250 µs 5 5.0 kHz 170 µs 12.7 bits 6 10 kHz 130 µs 11.8 bits 7 20 kHz 110 µs 10.6 bits

## **Output Response Time**

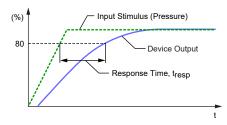

The output response time is the time interval between a) when input stimulus reaches 80% of its final value and b) the sensor reaches 80% of its final output, input signal being a step impulse (square signal).

Figure 4: Output Response Time Definition

## Power-On Time

Power-On Time is defined as the time it takes for the output to settle within  $\pm 10\%$  of its steady-state value under an applied stimulus (pressure), after the power supply has reached its minimum specified operating voltage,  $V_{CC}(min)$ .

Figure 5: Power-On Time Definition

## Front End Gain Adjustment

#### GAIN 1

The front end gain 1 amplifier can be adjusted with 2 bits to optimize the ADC input range and offset differential step.

| Table 2: | Front | End | Gain | 1 | Selection |

|----------|-------|-----|------|---|-----------|

|          |       |     |      |   |           |

| Coarse Gain Code | Gain 1 |

|------------------|--------|

| 0 (Default)      | 3      |

| 1                | 6      |

| 2                | 9      |

| 3                | 12     |

### GAIN 2

The front end gain 2 amplifier can be adjusted with 4 bits to further optimize ADC input range.

#### Table 3: Front End Gain 2 Selection

| Coarse Gain Code | Gain 2 |

|------------------|--------|

| 0 (Default)      | 1.0    |

| 1                | 1.4    |

| 2                | 1.8    |

| 3                | 2.2    |

| 4                | 2.6    |

| 5                | 3.0    |

| 6                | 3.4    |

| 7                | 3.8    |

| 8                | 4.2    |

| 9                | 4.6    |

| 10               | 5.0    |

| 11               | 5.4    |

| 12               | 5.8    |

| 13               | 6.2    |

| 14               | 6.6    |

| 15               | 7.0    |

## Front End Differential Offset Adjustment

The Differential signal offset can also be programmed with 6 bits to center signal to ADC input range. Differential ADC Input Voltage ( $V_{\rm IN\ ADC}$ ) can be derived from Equation 1.

The offset is also expressed in the function of bridge sensitivity for ease of use (See Table 4).

#### Table 4: Front End Offset selection

| Coarse         | Differential Offset (mV/V) |             |              |       |  |  |  |  |

|----------------|----------------------------|-------------|--------------|-------|--|--|--|--|

| Offset<br>Code | Gain 1 = 3×                | Gain 1 = 9× | Gain 1 = 12× |       |  |  |  |  |

| 0 (default)    | 0.0                        | 0.0         | 0.0          | 0.0   |  |  |  |  |

| 1              | 2.7                        | 1.3         | 0.9          | 0.7   |  |  |  |  |

| 2              | 5.4                        | 2.7         | 1.8          | 1.3   |  |  |  |  |

| 3              | 8.0                        | 4.0         | 2.7          | 2.0   |  |  |  |  |

|                |                            |             |              |       |  |  |  |  |

| 30             | 80.3                       | 40.2        | 26.8         | 20.1  |  |  |  |  |

| 31             | 83.0                       | 41.5        | 27.7         | 20.8  |  |  |  |  |

| 32             | -85.7                      | -42.8       | -28.6        | -21.4 |  |  |  |  |

| 33             | -83.0                      | -41.5       | -27.7        | -20.8 |  |  |  |  |

|                |                            |             |              |       |  |  |  |  |

| 61             | -8.0                       | -4.0        | -2.7         | -2.0  |  |  |  |  |

| 62             | -5.4                       | -2.7        | -1.8         | -1.3  |  |  |  |  |

| 63             | -2.7                       | -1.3        | -0.9         | -0.7  |  |  |  |  |

### Input Signal Range Calculation

Figure 6

ADC input range ( $V_{IN\_ADC}$  in Figure 6) can be calculated in function of differential input signal ( $V_{IN}$  in Figure 6) with the following Equation 1.

Equation 1:

```

V_{IN\_ADC} = Gain1 \times Gain2 \times [(V_{IN} + V_{BRG} \times OFFSET_{coarse}) \times (-1)^{polarity\_bit}]

```

where

Gain1 and Gain2 are respectively defined in Table 2 and Table 3,

Pol\_bit is the polarity bit,

OFFSET<sub>coarse</sub> is defined in Table 4 (mV/V), OFFSET<sub>coarse</sub> scales with Gain1

$V_{IN} = V_p - V_n (mV)$ , and

$V_{BRG}$  is bridge supply from A17700 (3.3 V typ).

$V_{IN ADC}$  could also be expressed in function of ADC<sub>IN</sub>:

$V_{IN ADC} = ADC_{IN} \times V_{BRG}.$

### **EXAMPLE OF SIGNAL RANGE CALCULATIONS**

Considering a bridge of the following characteristics:

Sensitivity: +35 mV/V

Offset: +10 mV/V

Maximum differential input value can be calculated as:

$$V_{IN MAX} = (BRG_{sens} + BRG_{off}) \times V_{BRG}$$

$BRG_{sens}$  being the bridge sensitivity (mV/V);  $BRG_{off}$  being the bridge offset (mV/V).

$$V_{IN MAX} = (0.035 + 0.010) \times 3.3 = 148.5 \text{ mV}$$

$V_{\text{IN MIN}} = (0 + 0.01) \times 3.3 = 33 \text{ mV}$

Therefore,  $V_{IN}$  will vary from 33 to 148.5 mV.

# EXAMPLE OF COARSE GAIN AND OFFSET CALCULATIONS

Gain is calculated first:

Equation 2:

Gain1 × Gain2 =

$$V_{IN ADC} / [(V_{IN} + V_{BRG} \times OFFSET_{coarse}) \times (-1)^{polarity_bit}]$$

Default OFFSET<sub>coarse</sub> value is 0, therefore:

$$Gain1 \times Gain2 = (V_{IN ADC(range)}) / (V_{IN} \times (-1)^{pol\_bit})$$

Focusing on signal range, where in this example, signal is unidirectional and anticipating for offset step size:

$$\begin{split} V_{IN\_ADC(range)} = & V_{IN\_ADC(max)} - V_{IN\_ADC(min)} - Offset_{STP} \times V_{BRG} \\ = & 2 \times V_{IN\_ADC(max)} - Offset_{STP} \times V_{BRG} \\ = & (2 \times ADC_{IN(max)}) - Offset_{STP}) \times V_{BRG}, \text{ and} \end{split}$$

$V_{IN(range)} = V_{IN(max)} - V_{IN(min)}$

Then:

$$\begin{aligned} Gain1 \times Gain2 &= 2 \times ADC_{IN} (max) \times V_{BRG} / [V_{IN(range)} \times (-1)^{pol\_bit}] \\ &= ((2 \times 0.263 - 0.0027) \times 3.3) / (0.1485 - 0.033) \times 1 = 14.9 \end{aligned}$$

This number can be obtained with default Gain1 code, thus:

Gain  $1 = 3\times$ , Gain 2 = 14.9/3 = 4.97 (code 9 is the matching lowest value).

Using this Gain configuration (Gain1 =  $3\times$ , Gain2 =  $4.6\times$ ) with OFFSET<sub>coarse</sub> = 0 gives the following ADC<sub>IN</sub> min/max values:

$$ADC_{IN} (max) = Gain1 \times Gain2 \times V_{IN}MAX / V_{BRG} = 621 mV/V$$

$ADC_{IN} (min) = Gain1 \times Gain2 \times V_{IN}MIN / V_{BRG} = 138 mV/V$

Gained-up signal must be centered to ADC input range using coarse offset compensation:

Total Offset = (621 + 138) / 2 = 379.5 mV/V, OFFSET<sub>coarse</sub> code =  $(-379.5 / (3 \times 4.6)) / 2.667 = -10.3 \leftrightarrow \text{code} -10$ .

Therefore, ADC<sub>IN</sub> min/max values become:

$ADC_{IN} (max) = 253 \text{ mV/V}$  $ADC_{IN} (min) = -230 \text{ mV/V}$

#### Fine Adjustment and Temperature Compensation

The A17700 uses an internal DSP to fine adjust offset and sensitivity and to compensate for nonlinearity over temperature. The compensation algorithm takes as inputs the pressure as sensed by the external pressure sensor (Wheatstone bridge) and the temperature as sensed by the internal temperature sensor. The DSP compensates the pressure with a polynomial function up to 4th order that also includes temperature.

Note that  $a_{00}$  is implicitly used to fine adjust the Offset and  $a_{10}$  is

implicitly used to fine adjust the Sensitivity.

$f(P_{SENSED}, T_{SENSED}) =$

- $a_{00} + a_{10} \ P_{SENSED} + a_{01} \ T_{SENSED}$

- $+ a_{20} P^2_{SENSED} + a_{11} P_{SENSED} T_{SENSED}$

- $+ a_{02} T^2_{\text{SENSED}} + a_{30} P^3_{\text{SENSED}}$

- $+ a_{21} P_{SENSED}^2 T_{SENSED} + a_{12} P_{SENSED} T_{SENSED}^2$

- $\begin{array}{l} + a_{03} \ T^3_{SENSED} + a_{40} \ P^4_{SENSED} \\ + a_{31} \ P^3_{SENSED} \ T_{SENSED} + a_{22} \ P^2_{SENSED} \ T^2_{SENSED} \\ + a_{13} \ P_{SENSED} \ T^3_{SENSED} + a_{04} \ T^4_{SENSED} \end{array}$

This function uses 15 coefficients for full flexibility and therefore at least 15 calibration points are also required. A lower degree polynomial compensation can also be used (Poly(3,3), Poly(2,4),etc.); in such cases, the higher degree coefficients must receive a 0 value.

Note that all coefficients are calculated externally and fed into A17700. A least-squares fit technique can be used to calculate coefficient. All coefficients should be a number between -1 and 1. To load a coefficient to the EEPROM, it must be multiplied by the fractional length  $(2^{15})$  and converted to a 16-bit two complement register.

Note: For optimized compensation, internal device temperature sensor input must be used.

#### **EXAMPLE OF POLYNOMIAL COEFFICIENT** CALCULATIONS

As input data, measurements at various temperatures and pressures must be performed. At each calibration point, the following two registers must be sampled with correct format:

#### Table 5

| Name         | Address        | Register<br>structure | Number of<br>bits | Fractional<br>length |  |

|--------------|----------------|-----------------------|-------------------|----------------------|--|

| adc_comp_reg | [15:0] at 0x52 | Signed                | 16                | 15                   |  |

| tt_comp_reg  | [11:0] at 0x62 | Signed                | 12                | 11                   |  |

Example: adc\_comp\_reg 0b1110 0011 1111 0010  $\rightarrow -0.219177246093750$ tt\_comp\_reg 0b0000 1010 0000 → 0.07812500000000

Denote the adc comp reg samples as p<sub>i</sub>, tt comp reg samples as t<sub>i</sub>, and the applied pressure [bar] as P<sub>i</sub>.

Then define variables for the least square fitting:

Matrix A:

$$A = \begin{bmatrix} 1 & p_1 & t_1 & p_1^2 & p_1 \cdot t_1 & t_1^2 & p_1^3 & p_1^2 \cdot t_1 & p_1 \cdot t_1^2 & t_1^3 & p_1^4 & p_1^3 \cdot t_1 & p_1^2 \cdot t_1^2 & p_1 \cdot t_1^3 & t_1^4 \\ 1 & p_2 & t_2 & p_2^2 & p_2 \cdot t_2 & t_2^2 & p_2^3 & p_2^2 \cdot t_2 & p_2 \cdot t_2^2 & t_2^3 & p_2^4 & p_2^3 \cdot t_2 & p_2^2 \cdot t_2^2 & p_2 \cdot t_2^3 & t_2^4 \end{bmatrix}$$

Vector b:

$$b = \begin{bmatrix} b_1 \\ b_2 \\ \dots \end{bmatrix}$$

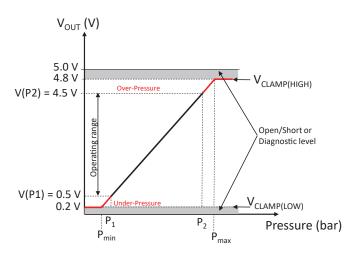

where  $b_i = 2 \cdot \left( \frac{V(P2) - V(P1)}{4.6} \cdot \frac{P_i - P1}{P2 - P1} + \frac{V(P1) - 0.2}{4.6} \right) - 1$ where P1 and P2 are the operating pressures limit in bar, and

V(P1) and V(P2) their corresponding voltages in volt.

The coefficients c are then derived by a bounded least square algorithm  $(-1 \le c \le 1)$ :

c = lsqr(A,b)

The second element in c, corresponding to  $a_{10}$ , must be decreased by a unity amount:

$$c(2) = c(2) - 1$$

Then, all the coefficients must be rescaled:

$c = 0.0625 \times c$

The coefficients are ready to be written to EEPROM with correct format:

#### Table 6

| Name            | Address        | Signedness | Number of<br>bits | Fractional<br>length |  |

|-----------------|----------------|------------|-------------------|----------------------|--|

| press_coeff_aXX | See memory map | Signed     | 16                | 15                   |  |

Example: press coeff a00 -0.001770019531250 → 0b1111 1111 1100 0110

## **Output Protocols**

### ANALOG OUTPUT MODE

The A17700 features an analog output, with the output voltage mapped proportionally to the compensated Wheatstone bridge output ( $V_P$ - $V_N$ ).

The analog output is ratiometric with  $V_{CC}$  for a more accurate reading and it includes programmable clamps for easy diagnostics.

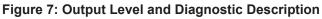

#### Clamps

The output voltage clamps,  $V_{CLAMP(HIGH)}$  and  $V_{CLAMP(LOW)}$ , are set in digital domain and limit the operating range of the applied input in which the device provides a linear output. Clamps can be programmed as per Table 7.

| Clamp-High<br>Code | V <sub>CLAMP(HIGH)</sub> | Unit             | Clamp-Low<br>Code | V <sub>CLAMP(Low)</sub> | Unit             |

|--------------------|--------------------------|------------------|-------------------|-------------------------|------------------|

| 0 (Default)        | 96                       | %V <sub>CC</sub> | 0 (Default)       | 4                       | %V <sub>CC</sub> |

| 1                  | 95                       | %V <sub>CC</sub> | 1                 | 5                       | %V <sub>CC</sub> |

| 2                  | 94                       | %V <sub>CC</sub> | 2                 | 6                       | %V <sub>CC</sub> |

| 3                  | 93                       | %V <sub>CC</sub> | 3                 | 7                       | %V <sub>CC</sub> |

| 4                  | 92                       | %V <sub>CC</sub> | 4                 | 8                       | %V <sub>CC</sub> |

| 5                  | 91                       | %V <sub>CC</sub> | 5                 | 9                       | %V <sub>CC</sub> |

| 6                  | 90                       | %V <sub>CC</sub> | 6                 | 10                      | %V <sub>CC</sub> |

| 7                  | 89                       | %V <sub>CC</sub> | 7                 | 11                      | %V <sub>CC</sub> |

| 8                  | 88                       | %V <sub>CC</sub> | 8                 | 12                      | %V <sub>CC</sub> |

| 9                  | 87                       | %V <sub>CC</sub> | 9                 | 13                      | %V <sub>CC</sub> |

| 10                 | 86                       | %V <sub>CC</sub> | 10                | 14                      | %V <sub>CC</sub> |

| 11                 | 85                       | %V <sub>CC</sub> | 11                | 15                      | %V <sub>CC</sub> |

| 12                 | 84                       | %V <sub>CC</sub> | 12                | 16                      | %V <sub>CC</sub> |

| 13                 | 83                       | %V <sub>CC</sub> | 13                | 17                      | %V <sub>CC</sub> |

| 14                 | 82                       | %V <sub>CC</sub> | 14                | 18                      | %V <sub>CC</sub> |

| 15                 | 81                       | %V <sub>CC</sub> | 15                | 19                      | %V <sub>CC</sub> |

| 16                 | 80                       | %V <sub>CC</sub> | 16                | 20                      | %V <sub>CC</sub> |

| 17                 | 79                       | %V <sub>CC</sub> | 17                | 21                      | %V <sub>CC</sub> |

| 18                 | 78                       | %V <sub>CC</sub> | 18                | 22                      | %V <sub>CC</sub> |

| 19                 | 77                       | %V <sub>CC</sub> | 19                | 23                      | %V <sub>CC</sub> |

| 20                 | 76                       | %V <sub>CC</sub> | 20                | 24                      | %V <sub>CC</sub> |

| 21                 | 75                       | %V <sub>CC</sub> | 21                | 25                      | %V <sub>CC</sub> |

| 22                 | 74                       | %V <sub>CC</sub> | 22                | 26                      | %V <sub>CC</sub> |

| 23                 | 73                       | %V <sub>CC</sub> | 23                | 27                      | %V <sub>CC</sub> |

| 24                 | 72                       | %V <sub>CC</sub> | 24                | 28                      | %V <sub>CC</sub> |

| 25                 | 71                       | %V <sub>CC</sub> | 25                | 29                      | %V <sub>CC</sub> |

| 26                 | 70                       | %V <sub>CC</sub> | 26                | 30                      | %V <sub>CC</sub> |

| 27-31              | 70                       | %V <sub>CC</sub> | 27-31             | 30                      | %V <sub>CC</sub> |

| Table | 7: | Clamp | Programming |

|-------|----|-------|-------------|

|-------|----|-------|-------------|

Values outside of the mapping range are used as the diagnostic signal indicating a malfunction of the device. When an external pull-up or pull-down is used, and an invalid mode is detected (i.e. short/broken bridge wire, under/overvoltage, ECC memory error, etc.) while diagnostics are enabled, the output will go to a high-impedance state.

With appropriate poly coefficients programmed to the device, the output can be set so that over-pressure or under-pressure can be diagnosed in addition to open/short wire or diagnostic detection. For example, a device could be trimmed so that output at P1 gives 10%  $V_{CC}$  and output at P2 equals 90%  $V_{CC}$ , while the clamps are set to 4 to 96%. In this case, output between 4 and 10%  $V_{CC}$  would reveal under-pressure (pressure < P1) fault, while output between 90 and 96%  $V_{CC}$  would reveal over-pressure (pressure > P2) fault. Output higher than 96%  $V_{CC}$  or lower than 4%  $V_{CC}$  informs that an open/short event occurred or that a diagnostic flag was raised (assuming diagnostic enabled). This is illustrated in Figure 7.

## **Ratiometry Error**

The A17700 device features ratiometric output. This means that the Output and Clamp voltages are proportional to the supply voltage. When the supply voltage increases or decreases by a certain percentage, each characteristic also increases or decreases by the same percentage. Error is the difference between the measured change in the supply voltage relative to 5 V and the measured change in each characteristic.

The ratiometric error in voltage output,  $Rat_{ERRVOUT(Q)}$  (%), for a given supply voltage,  $V_{CC},$  is defined as:

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

$$\operatorname{Rat}_{\operatorname{ERRVOUT}(Q)} = \left(\frac{V_{\operatorname{OUT}(Q)(\operatorname{VCC})} / V_{\operatorname{OUT}(Q)(5\operatorname{V})}}{V_{\operatorname{CC}} / 5\operatorname{V}}\right) \times 100 \ (\%)$$

where  $V_{OUT(Q)}$  is the output when the bridge doesn't output differential signal.

The ratiometric error in clamp voltages,  $Rat_{ERRCLP}$  (%), for a given supply voltage,  $V_{CC}$ , is defined as:

$$\operatorname{Rat}_{\operatorname{ERRCLP}} = \left(\frac{V_{\operatorname{CLP}(\operatorname{VCC})} / V_{\operatorname{CLP}(5\operatorname{V})}}{V_{\operatorname{CC}} / 5\operatorname{V}}\right) \times 100 \ (\%)$$

where  $V_{CLP}$  is either  $V_{CLAMP(HIGH)}$  or  $V_{CLAMP(LOW)}$ .

#### Linearity Sensitivity Error

The A17700 is designed to provide a compensated linear output in response to a ramping differential signal at pins  $V_P$ - $V_N$ .

INL, Integral Non-Linearity, is a common performance measurement for DACs. It is the deviation between the ideal output values and the actual measured value once offset and gain have been accounted for. The equation below shows how this value was calculated:

INL =

$$\frac{(V_{OUT}(c_i) - V_{OUT}(c_{min}) - (c_i - c_{min}) \times RefStep)}{RefStep}$$

where  $c_i$  is the input code and  $c_{min}$  is the minimum input code.

Reference step (RefStep) is the step size of the DAC in terms of analog value per bit. It is calculated as shown below.

$$RefStep = \frac{(V_{OUT}(c_{max}) - V_{OUT}(c_{min}))}{(c_{max} - c_{min})}$$

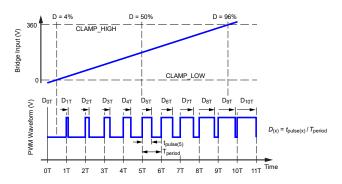

#### **PWM OUTPUT MODE**

PWM involves converting the output signal amplitude to a series of constant-frequency binary pulses, with the percentage of the high portion of the pulse directly proportional to the signal amplitude.

PWM carrier frequency is programmable from 0.250 kHz to 16 kHz for easier detection (refer to Table 8 for available options).

PWM uses clamps similarly to the analog output to limit the output range and for diagnostic purpose. Devices can be tuned to a maximum  $PWM_{CLAMP(H)}$  value of 96% and a minimum  $PWM_{CLAMP(L)}$  value of 4% DC (see Figure 8).

Figure 8: PWM Output Mode - Duty-Cycle-Based Waveform

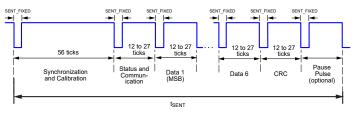

#### SENT OUTPUT MODE

The SENT output mode converts the input bridge signal to a binary value mapped to the Full-Scale Output, FSO, for a range of 0 to 4095 as shown in Figure 9. This data is inserted into a binary pulse message, referred to as a frame, which conforms to the SENT data transmission specification (SAEJ2716). Certain parameters for configuration of the SENT messages can be set in EEPROM.

The SENT output modes are selected using the dig\_out\_mode EEPROM parameters:

- dig\_out\_mode = 2: SENT output as per SAEJ2716 (no Pause Pulse)

- dig\_out\_mode = 3: SENT output with Pause Pulse

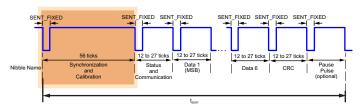

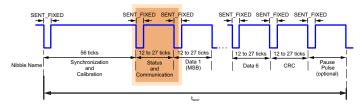

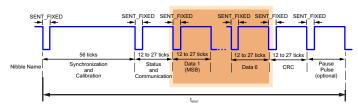

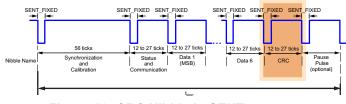

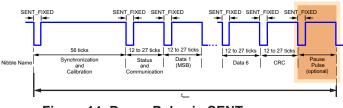

#### **SENT Message Structure**

A SENT message is a series of nibbles with the following characteristics:

- Each nibble is an ordered pair of a low-voltage interval followed by a high-voltage interval.

- The low interval, SENT\_FIXED, is defined as 5 SENT ticks. The high interval contains information and is variable in duration to indicate the data payload of the nibble.

Figure 9: SENT Message

The duration of a nibble is denominated in clock ticks. The period of a tick is set by the Out\_freq\_rate parameter defined in Table 8.

The duration of the nibble is the sum of the low-voltage interval plus the high-voltage interval.

The nibbles of a SENT message are arranged in the following required sequence:

- 1. Synchronization and Calibration: flags the start of the SENT message

- 2. Status and Communication: provides A17700 status and the format of the data

- 3. Data: pressure and optional data

- 4. CRC: error checking

- 5. Pause Pulse (optional): sets timing relative to A17700 updates

| Out_freq_rate<br>Code |      |       |    |

|-----------------------|------|-------|----|

| 0 (default)           | 3    | 1000  | 12 |

| 1                     | 5    | 250   | 12 |

| 2                     | 2.5  | 500   | 12 |

| 3                     | 2    | 1600  | 12 |

| 4                     | 1.5  | 2667  | 12 |

| 5                     | 1    | 4000  | 11 |

| 6                     | 0.75 | 8000  | 10 |

| 7                     | 0.5  | 16000 | 9  |

#### Table 8: SENT/PWM rate parameters

#### Synchronization and Calibration Pulse

# Figure 10: Synchronization and Calibration Pulse in SENT Message

The Synchronization and Calibration pulse is 56 ticks wide, measured from falling edge to falling edge, and delineates the start of a new message frame. The host microcontroller uses this pulse to rescale the subsequent nibble values to correct for clock variation between the controller and the sensor.

#### Status and Communication Nibble

#### Figure 11: SCN Nibble in SENT Message

The Status and Communication Nibble (SCN) provides diagnostic information along with optional other data from the short serial message. Nibble contents are controlled via the SCN\_ MODE field within EEPROM (See Table 9).

By default, contents of the SCN are not included in the 4-bit CRC at the end of each SENT frame. The SENT\_SCN\_CRC bit within EEPROM enables CRC coverage of the SCN contents. It should be noted that this option is not specified in the SAEJ2716 SENT standard. With the SENT\_SCN\_CRC bit set, the CRC is no longer compliant with that outlined in the SENT specification.

| Table 9: Status and | <b>Communication</b> | Nibble (S | SCN) modes |

|---------------------|----------------------|-----------|------------|

|---------------------|----------------------|-----------|------------|

| SCN Mode    | Bit 3       | Bit 2       | Bit 1 | Bit 0 |

|-------------|-------------|-------------|-------|-------|

| 0 (default) | 0           | 0           | Err   | 0     |

| 1           | Serial sync | Serial data | Err   | 0     |

| 2           | Serial sync | Serial data | 0     | 0     |

| 3           | 0           | 0           | 0     | 0     |

The SCN has two different types of bit values that may be present, depending on the SCN\_MODE setting. These are:

#### Error Bit

This bit is latched to 1 temporarily, and is cleared on the following SENT frame, unless fault is still asserted and considering that any of the following diagnostics are enabled: Undervoltage, Overvoltage, Overtemperature, Undertemperature, Signal out of Range, Open/Short Bridge.

Note that multi-bit EEPROM fault will trigger high-impedance output state.

### Serial Data

Two bits, consisting of the SerialSync and SerialData bits. Together they form the Short Serial Message (per SAEJ2716 Section 5.2.4.1).

SerialSync: Indicates the start of a 16-bit serial message.

SerialData: Serial data, transmitted one bit at a time, MSB first.

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

### **Optional Short Serial Message**

The A17700 SENT output supports an optional mode to transmit additional data: the slow serial mode. It enables transmission of additional data by encoding information in the Status and Communication (SCN) nibbles. A 16-bit data packet is transmitted one bit at a time over consecutive SENT message frames, starting with the MSB. The beginning of each 16-bit packet is indicated by a "1" in the SerialSync bit. The message data is transmitted bit-by-bit via the SerialData bit (See Table 10 for Short Serial Message Format).

The slow serial mode is enabled when the EEPROM parameter SCN\_mode is set to 1 or 2. Following a reset, the first message transmitted is 0, following in order of the message ID until message 4, and then repeating. Table 11 identifies the data sent with each message ID. The CRC for the Short Serial Message is derived for the Message ID and data, and is the same checksum algorithm used for the SENT CRC.

#### Table 10: Short Serial Message Format in SCN Nibble

| SNC Bit    |    | Frame # |     |   |      |   |   |   |    |    |    |    |    |    |    |    |

|------------|----|---------|-----|---|------|---|---|---|----|----|----|----|----|----|----|----|

|            | 1  | 2       | 3   | 4 | 5    | 6 | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| SerialSync | 1  | 0       | 0   | 0 | 0    | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| SerialData | Me | ssag    | elD |   | Data |   |   |   | CF | RC |    |    |    |    |    |    |

#### Table 11: Serial Output Data

| Message ID | Data                                         |

|------------|----------------------------------------------|

| 0          | 9-bit diagnostics, MSB always 0              |

| 1          | 9-bit internal temperature                   |

| 2          | 9-bit customer scratch [8:0]                 |

| 3          | 9-bit customer scratch [17:9]                |

| 4          | 9-bit customer scratch [25:18], MSB always 0 |

#### **SENT Data Nibble Format**

#### Figure 12: Data Nibble in SENT message

The A17700 supports options for the message data nibble format. The data nibble format is determined by the EEPROM parameter sent\_data\_cfg. The options for a minimum 3 or maximum 6 nibbles are defined in SENT data table (Table 12). For each option,

data to be transmitted is sampled at the end of the SCN nibble.

Note that sent\_data\_cfg = 3 has the same effect as sent\_data\_cfg = 2.

| Table | 12: | SENT | Data | Config |

|-------|-----|------|------|--------|

|-------|-----|------|------|--------|

| sent_data_<br>cfg | Data Nibble<br>#1  | Data Nibble<br>#2 | Data Nibble<br>#3 | Data Nibble<br>#4 | Data Nibble<br>#5 | Data Nibble<br>#6 | # of<br>Nibbles |

|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------|

| 0 (default)       | Pressure<br>[11:8] | Pressure<br>[7:4] | Pressure<br>[3:0] | -                 | -                 | -                 | 3               |

| 1                 | Pressure<br>[11:8] | Pressure<br>[7:4] | Pressure<br>[3:0] | Diag<br>[7:4]     | Diag<br>[3:0]     | -                 | 5               |

| 2                 | Pressure<br>[11:8] | Pressure<br>[7:4] | Pressure<br>[3:0] | IntTemp<br>[11:8] | IntTemp<br>[7:4]  | IntTemp<br>[3:0]  | 6               |

#### SENT CRC Nibble

#### Figure 13: CRC Nibble in SENT message

The CRC nibble is a 4-bit error checking code, implemented per the SAEJ2716 SENT "recommended" specification.

The CRC is calculated using the polynomial  $x^4 + x^3 + x^2 + 1$ , initialized to 0101.

By default, the checksum covers only the contents of the data nibbles (3-6 nibbles). By setting the SENT\_SCN\_CRC bit within EEPROM, the contents of the SCN are included within the CRC nibble which deviates from the SENT standard.

#### SENT Pause Pulse

Figure 14: Pause Pulse in SENT message

The Pause Pulse is an optional addition to the SENT message frame, transmitted following the CRC nibble. It acts to "fill-in" the frame until the beginning of the next SENT transmission in order to have constant output rate. The inserted Pause Pulse is a minimum of 12 Ticks in length. The frame duration is always:

Frame Duration (ticks) =  $56 + (N + 2) \times 27 + 12$

where N is the number of data nibbles in the frame.

## **Digital Output Mode Selection**

Digital Output mode can be selected according to Table 13. Table 13: Digital Output Modes Selection

| dig_out_mode code | Output Type Description                             |

|-------------------|-----------------------------------------------------|

| 0 (default)       | PWM output with PWM level diagnostic reporting      |

| 1                 | PWM output with high impedance diagnostic reporting |

| 2                 | SENT output (no pause pulse)                        |

| 3                 | SENT output with pause pulse                        |

## **Digital Output Driver Fall Time Selection**

User is allowed to change the fall time of the output digital signal using the EEPROM parameter Out\_drive\_sel. User must ensure that "Sent\_ftc\_e\_n" bit is set to 0 so that the changes to output driver apply.

| Out_drive_sel | Time from 90% to 10%,<br>C <sub>L</sub> = 100 pF<br>(μs) |

|---------------|----------------------------------------------------------|

| 0 (default)   | 0.11                                                     |

| 1             | 0.18                                                     |

| 2             | 0.27                                                     |

| 3             | 0.35                                                     |

| 4             | 0.7                                                      |

| 5             | 1.24                                                     |

| 6             | 2.42                                                     |

| 7             | 3.55                                                     |

#### **Table 15: Output Diagnostics**

### **Broken Wire Detection**

The A17700 contains circuitry to detect a condition when the ground or supply connection is disconnected. When the device is connected as per the recommended application circuit (Figure 2), the output will go to Vsat\_diag\_H in case of broken ground and Vsat\_diag\_L in case of broken VCC.

## **Diagnostic Features**

The A17700 is equipped with diagnostic features enabling the host microcontroller to assess the operational status of sensor and device. These diagnostics can be activated through individual EEPROM bits and are summarized in Table 15.

#### **DIAGNOSTIC REPORTING**

When the device detects one of the fault given in Table 15 (except for Memory ECC fault), it will set a flag in a volatile register that can be cleared when the fault is removed through a register read (or reset) or after being sent out through the output protocol. This volatile register can be accessed through Manchester protocol. Reporting to device output depends on output protocol.

In analog output mode or in PWM mode with dig\_out\_mode = 1, the device output will hold the diagnostic state (high impedance) until the fault is removed or for a minimum of 4 ms to allow for appropriate detection.

High impedance state is factory configurable and could be adjusted on customer demand. Contact Allegro for further information.

| Diagnostic Detection              | Conditions                                | Analog Output State | PWM Output State<br>dig_out_mode = 0<br>(Reporting Priority) | PWM Output State<br>dig_out_mode = 1 | SENT Data Nibble #4 and #5<br>SENT_data_cf = 1<br>dig_out_mode = 2 or 3 | SENT SCN Nibble<br>All SENT_data_cf options<br>dig_out_mode = 2 or 3<br>SCN mode = 0 or 1 |

|-----------------------------------|-------------------------------------------|---------------------|--------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Memory ECC                        | Multi-bit EEPROM Error                    | High Impedance      | High Impedance (1)                                           | High Impedance                       | High Impedance                                                          | High Impedance                                                                            |

| Undervoltage Condition            | Undervoltage detection<br>is enabled      | High Impedance      | 1/2 carrier frequency,<br>20% DC (2)                         | High Impedance                       | xxxx xx1x                                                               | xx1x                                                                                      |

| Overvoltage Condition             | Overvoltage detection<br>is enabled       | High Impedance      | 1/2 carrier frequency,<br>30% DC (3)                         | High Impedance                       | xxxx x1xx                                                               | xx1x                                                                                      |

| Overtemperature Condition         | Overtemperature detection<br>is enabled   | High Impedance      | 1/2 carrier frequency,<br>40% DC (4)                         | High Impedance                       | xxxx 1xxx                                                               | xx1x                                                                                      |

| Undertemperature Condition        | Undertemperature detection is enabled     | High Impedance      | 1/2 carrier frequency,<br>60% DC (5)                         | High Impedance                       | xxx1 xxxx                                                               | xx1x                                                                                      |

| Input Signal Out of Range         | Input Signal Out of Range<br>is enabled   | High Impedance      | 1/2 carrier frequency,<br>70% DC (6)                         | High Impedance                       | xx1x xxxx                                                               | xx1x                                                                                      |

| Short/Broken Bridge<br>Connection | Bridge Short/Open detection<br>is enabled | High Impedance      | 1/2 carrier frequency,<br>80% DC (7)                         | High Impedance                       | x1xx xxxx                                                               | xx1x                                                                                      |

| DAC interpolator error            | DAC interpolator detection is<br>enabled  | High Impedance      | Not applicable                                               | Not applicable                       | Not applicable                                                          | Not applicable                                                                            |

In PWM output mode with dig\_out\_mode = 0, the device output will hold the diagnostic state until the fault is removed or for a minimum of 5 ms to allow for appropriate detection. If PWM carrier frequency was set to 500 Hz or lower, the fault state will be maintained for a minimum of 16 ms to allow for diagnostic reporting for at least 2 cycles.

The reporting priority in PWM mode with dig\_out\_mode = 0 refers to the situation where multiple faults are detected at the same time. In this case, only the fault with highest priority (i.e., number 1 is the highest) will be reported.

In SENT output mode, depending on selected SENT configuration, the diagnostic flags can be reported through SCN bit 1, through the short serial message, or through the SENT data nibble 4 and 5 (sent\_data\_cfg = 1). When fault is removed, the error flag register is cleared when the flag is transmitted through SENT message. Each of these three SENT reporting modes have individual flag registers so that they can be cleared independently.

#### **DIAGNOSTIC DESCRIPTION**

#### **Undervoltage Detection (UVD)**

The A17700 contains circuitry to continuously check if the supply voltage drops below the specified limit. Hysteresis is designed into the circuit to prevent chattering around the threshold. This hysteresis is defined by  $V_{UVD(R)} - V_{UVD(F)}$ . As an example, initially  $V_{CC}$  and  $V_{OUT}$  are within the normal operating range. If  $V_{CC}$  drops below  $V_{UVD(F)}$ , and assuming this diagnostic is activated through the EEPROM bit,  $V_{OUT}$  is forced to a state as defined in Table 15. When  $V_{CC}$  returns above  $V_{UVD(R)}$ ,  $V_{OUT}$  returns to its normal operating state after register read or reporting flags through the output modes, which will clear the error flag. If  $V_{CC}$  drops below the internal reset level,  $V_{POR(F)}$ , the output is forced to a high-impedance state. When  $V_{CC}$  returns above the rising reset level,  $V_{POR(R)}$ , the output responds with the UVD flag if enabled. To avoid setting UVD by incidental supply flickering, entering the UVD state is suppressed for approximately 20 µs.

#### **Overvoltage Detection (OVD)**

The A17700 contains circuitry to continuously check if the supply voltage rises above the specified limit. Hysteresis is designed into the circuit to prevent chattering around the threshold. This hysteresis is defined by  $V_{OVD(R)} - V_{OVD(F)}$ . As an example, initially  $V_{CC}$  and  $V_{OUT}$  are within the normal operating range. If  $V_{CC}$  rises above  $V_{OVD(R)}$ , and assuming this diagnostic is activated through the EEPROM bit,  $V_{OUT}$  is forced to a state as defined in Table 15. When  $V_{CC}$  returns below  $V_{OVD(F)}$ ,  $V_{OUT}$  returns to its normal operating state after register read or reporting flags through the output modes, which will clear the error flag. To avoid setting OVD by incidental supply flickering, entering the OVD state is suppressed for approximately 20  $\mu$ s.

In the case where OVD is disabled (EEPROM bit set to 0) but MANCH\_TRIGGER\_DIS = 00 or 01 and output is in digital mode, an OVD event will bring the device to communication mode and output will be forced to high impedance.

OVD threshold can be adjusted through EEPROM bit as per Table 16.

| Table | 16: | OVD | Level | Config |

|-------|-----|-----|-------|--------|

|-------|-----|-----|-------|--------|

| OVD_CFG     | OVD Rising<br>Threshold (typ) (V) | OVD Falling<br>Threshold (typ) (V) |

|-------------|-----------------------------------|------------------------------------|

| 0 (Default) | 5.8                               | 5.6                                |

| 1           | 6.3                               | 6.1                                |

| 2           | 6.8                               | 6.6                                |

| 3           | 6.8                               | 6.6                                |

#### **Overtemperature Detection (OTD)**

The OTD flag is set if the temperature sensor output saturates high, which indicates the ambient temperature is greater than 165°C (default value). This assumes diagnostic reporting was activated through EEPROM bit. If this condition occurs, the OTD flag will be set and the device will go into a state as defined in Table 15. If the temperature is detected to recover, a read of the device register or reporting through the output modes will clear the error flag so normal operation can resume. The OTD error can be detected every 8 ms and is never filtered.

#### **Undertemperature Detection (UTD)**

The UTD flag is set if the measured temperature is less than  $-70^{\circ}$ C (default value). If this condition occurs, the UTD flag will be set and the device will go into a state as defined in Table 15. If the temperature is detected to recover, a read of the device register or reporting through the output modes will clear the error flag so normal operation can resume. The UTD error can be detected every 8 ms and is never filtered.

OTD and UTD thresholds can be adjusted through EEPROM bit as per Table 17.

# Pressure Sensor Interface and Signal Conditioning IC with Polynomial Signal Compensation and Advanced Diagnostics

| Table 17: 0 | OTD/UTD | Level Config |

|-------------|---------|--------------|

|-------------|---------|--------------|

| OTD_CFG     | Overtemperature<br>Threshold (°C) | UTD_CFG     | Undertemperature<br>Threshold (°C) |

|-------------|-----------------------------------|-------------|------------------------------------|

| 0 (default) | 165                               | 0 (default) | -70                                |

| 1           | 160                               | 1           | -65                                |

| 2           | 155                               | 2           | -60                                |

| 3           | 150                               | 3           | -55                                |